2. Архитектура сетевых устройств

Итак, что такое сетевое устройство?

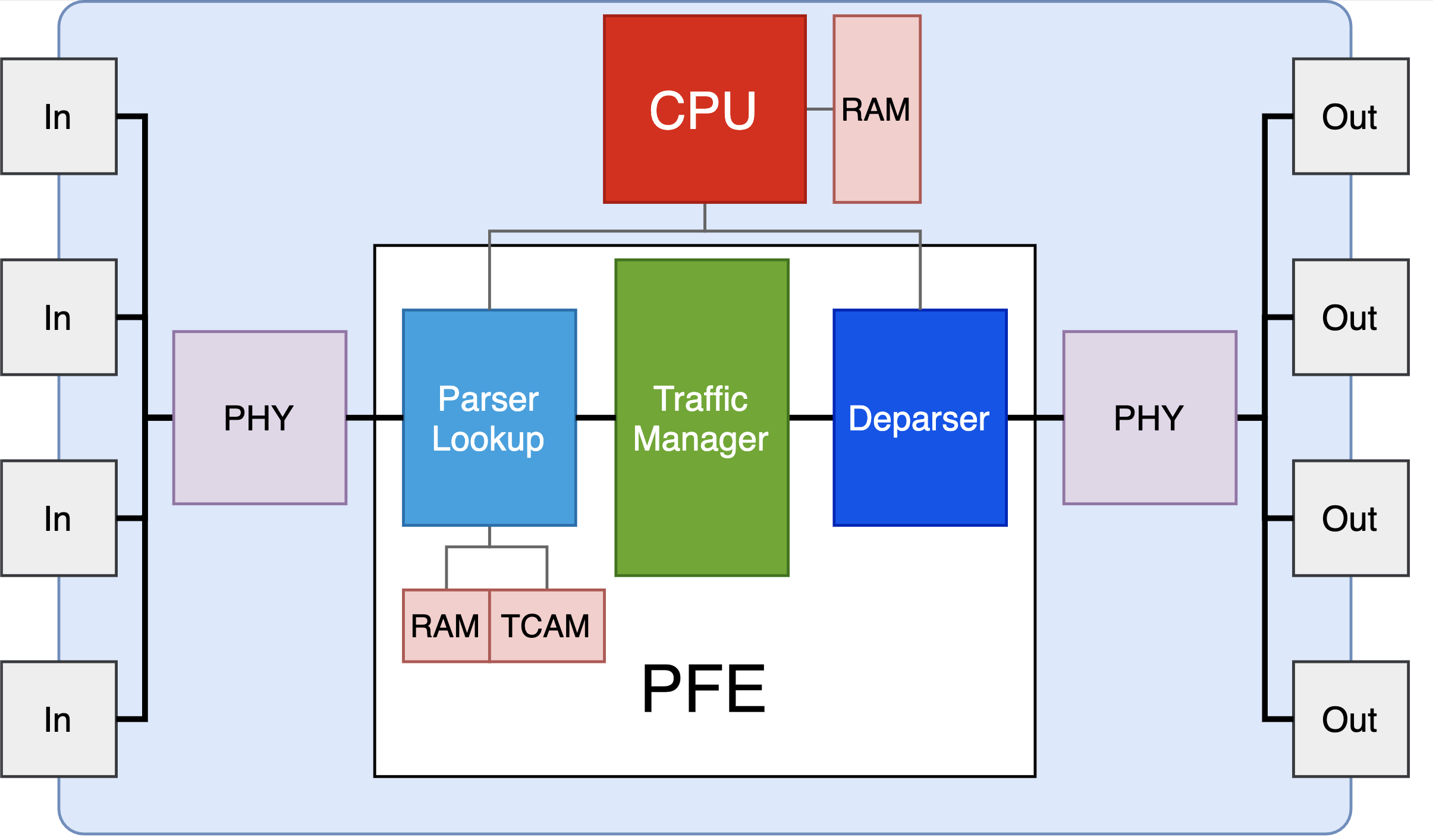

Будь то коммутатор, маршрутизатор, файрвол, балансировщик, программный или аппаратный, его задача - доставить пакет со входа на правильный выход, и состоит оно из следующих частей:

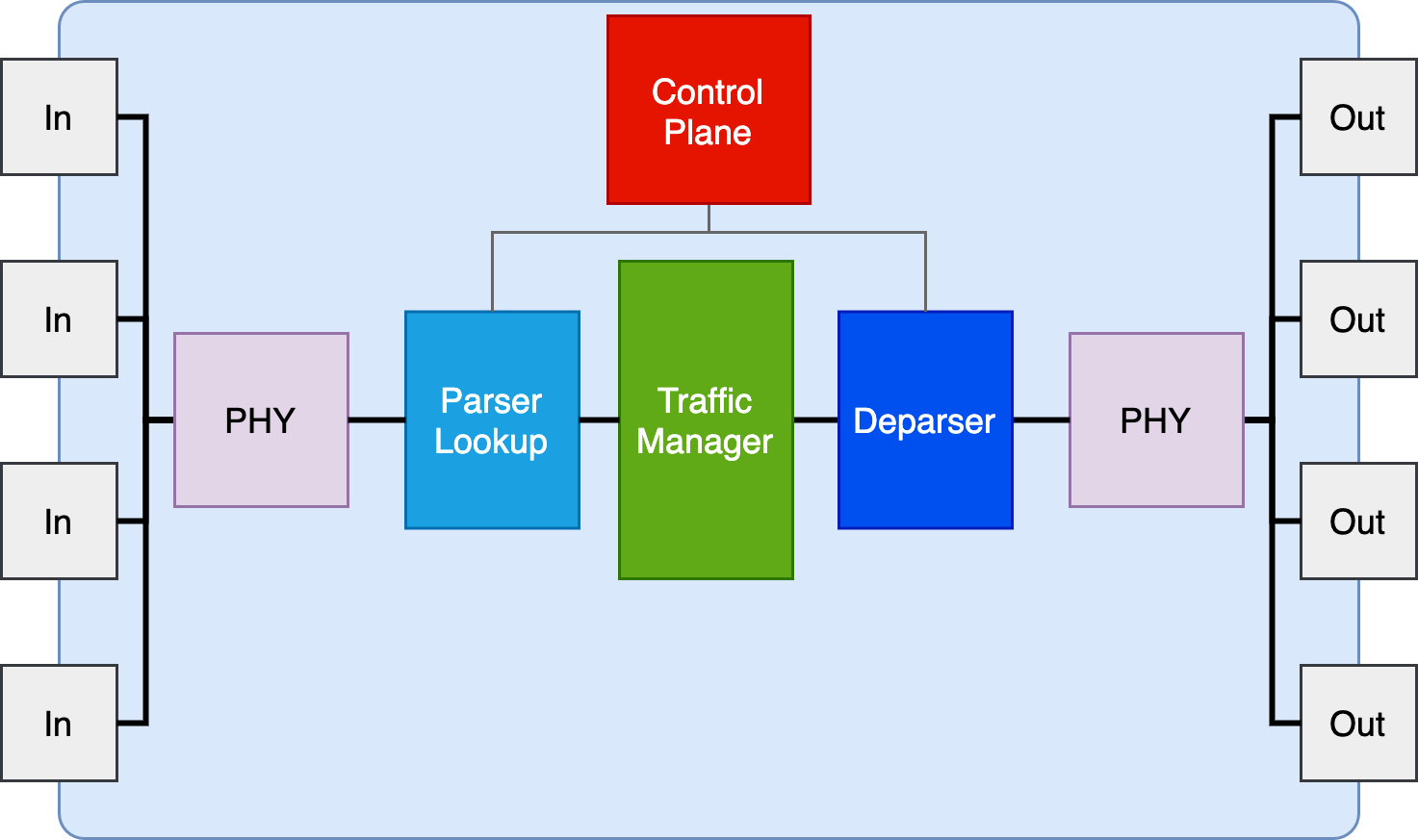

Электрический или оптический сигнал, попадая на устройство через входной физический порт, восстанавливается до потока битов, из него вычленяются отдельные Ethernet-кадры, далее на основе заголовков (Ethernet, IP, MPLS итд) (или иногда содержимого) принимается решение о том, в какой выходной порт этот пакет должен быть далее отправлен и с каким набором заголовков. На своём пути от входного к выходному порту пакет ещё проходит через модуль Traffic Manager, где с ним могут происходить следующие вещи: буферизация, полисинг, шейпинг, обработка по приоритетам.

Это путь самого пакета.

И отдельно от пути пакета - Control Plane Module, который отвечает за то, чтобы путь вообще появился. Это всяческие протоколы маршрутизации, обмена меток и прочее.

Это компоненты, которые присутствуют всегда и во всех сетевых устройствах.

Реализация же этих функций уже зависит от того, о чём именно мы говорим.

Например, на обычном x86 всю работу, кроме PHY могут взять на себя CPU и оперативка.

Более типично, что функции канального уровня заберёт на себя NIC - Ethernet, проверка контрольных сумм.

А можно в компьютер доставить SmartNIC’и, которые аппаратно могут делать, например, туннелирование.

Но мы не будем сегодня про программные реализации сетевых функций. Поговорим о старых добрых материальных коробках, которым всё равно никуда никогда не деться.

Вообще об этом я уже писал, поэтому повторяться не буду. Точнее буду, но не сильно. Точнее сильно, но я добавлю здесь ещё смысла.

Обычно на каждый блок задач выделяется специализированный чип.

Так, всем Control Plane’ом занимаются всё те же CPU + память.

Организация взаимодействия со средой передачи и преобразование битов в сигнал и наоборот - специальные чипы PHY. Почти всегда они реализуются на ASIC.

Разбор заголовков и поиск пути - Packet Forwarding Engine. Это может быть ASIC, Network Processor, реже FPGA и даже CPU. К ним в помощь идёт или обычная память RAM или специальная CAM/TCAM для хранения таблиц лукапа.

Traffic Manager - если вынесен отдельно, то опять же - узкоспециализированные ASIC’и и плюс к ним память. Но может быть встроенным в чип коммутации.

Один из вариантов реализации (single-chip устройство):

На этом этапе важно понять принципиальную разницу между плоскостями внутри устройства:

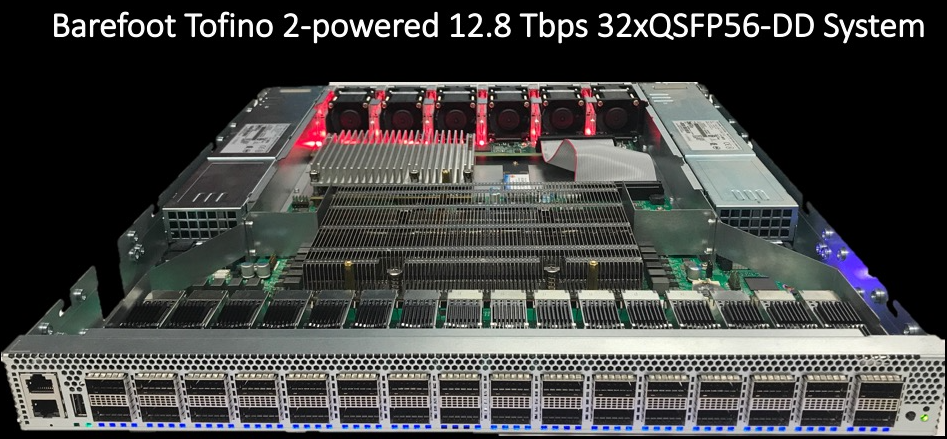

И перед тем, как продолжить, взглянем на то, как выглядят модульные коробки:

Поскольку вся книга посвящена обработке и хранению пакетов, я сосредоточусь на PFE и TM, которые и могут вносить вариативные задержки в доставку.