Логическое устройство¶

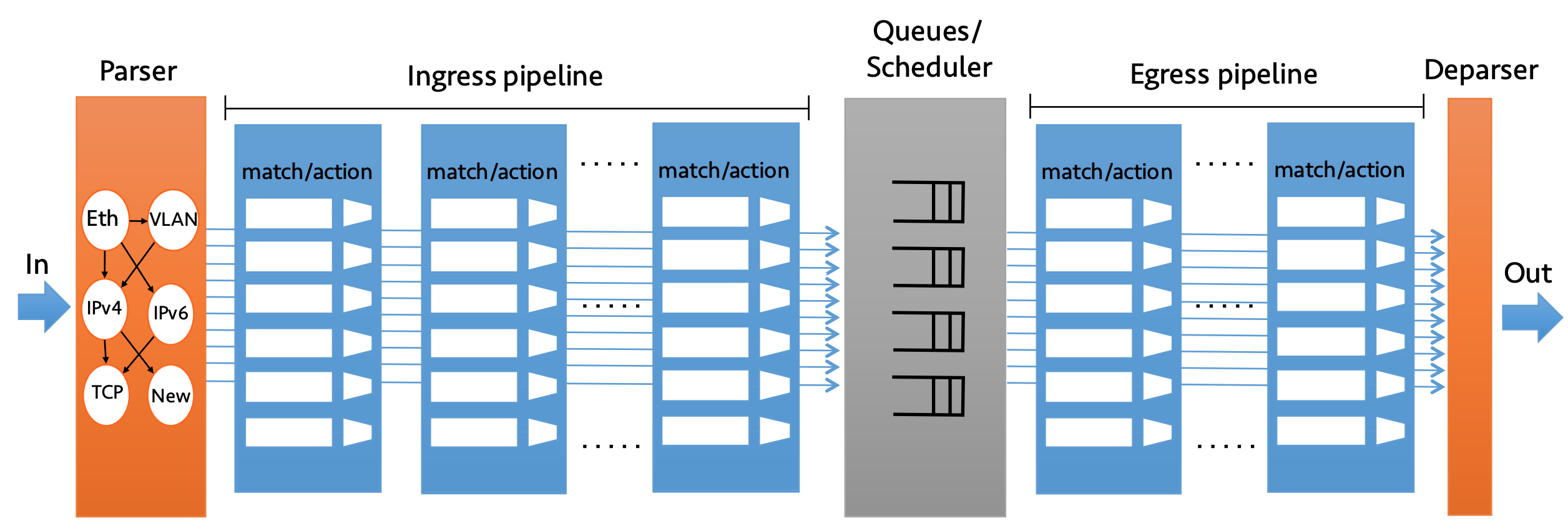

Типичный сетевой ASIC представляет из себя конвейер, по которому пакет передаётся от входного интерфейса к выходному, а по пути с ним случаются приключения. Английский термин для этого - Pipeline.

Хотя с виду и не скажешь:

В самом общем виде Pipeline выглядит так:

Пакет проходит через все стадии как минимум один раз, но для реализации сложных действий, вроде дополнительной инкапсуляции (VXLAN), может отправиться повторно.

Parser¶

Сначала на вход попадает пакет с неизвестным набором заголовков. Парсер разбирает все заголовки, отделяя их от собственно данных. Если это L2-коммутатор, то его заинтересует только заголовки Ethernet и VLAN. Если это MPLS-коммутатор, он заглянет в MPLS заголовки. Для L3 соответственно IPv4 и IPv6. Если это VXLAN-терминатор, ему понадобится UDP и собственно заголовок VXLAN. Для целей ECMP и ACL, парсер заглянет в UDP/TCP.

Строго говоря, на какие заголовки и какие поля в них надо смотреть, определяет фантазия разработчика. Сколько заголовков забрать? Как правило парсер вынимает фиксированное для чипа значение байтов от пакета и разделывает уже их. И это значение является одним из ограничений чипа.

Почему парсинг заголовков задача нетривиальная рассказывается в совместном исследовании Стэнфорда и Майкрософта: Design Principles for Packet Parsers.

Pre-Ingress processing¶

Иногда логически выделяют этот блок, который совершает действия, не являющиеся ни парсингом, ни как таковым лукапом - он кладет пакет в нужный VRF, ставит внутренний Traffic Class итд.

Ingress Match-Action¶

Когда парсер, разобрался с чем он имеет дело, он передаёт заголовки дальше - в модули Match-Action. Здесь происходит lookup. Для L2 поищем MAC’и, для L3 - прошерстим FIB, для MPLS - просмотрим в LFIB. И здесь же принимается решение, что с пакетом делать дальше: доложить CPU, пропустить/дропнуть, побалансировать, в какой порт отправить, какие заголовки навесить, с каким приоритетом внутри чипа обработать, полисить ли/шейпить ли его итд.

Собственно действие записано в той же таблице, в которой происходит lookup.

Это если коротко. А если чуть подлиннее, то:

L2 short pipeline¶

Приходящий L2-пакет всегда ассоциируется с VLAN. Тег VLAN проверяется через VLAN Lookup Table. Если VLAN lookup успешен, просматриваются таблицы: VLAN STP, VLAN Port Bitmap, Port Filtering Mode (PFM). Если же тег неверный, то пакет сбрасывается (или нет). После пакет проходит стандартную обработку: запомнить SRC MAC, посмотреть в таблице DST MAC, - но при этом могут быть применены дополнительные флаги, например, отправить на CPU unknown sender.

L3 short pipeline¶

Если DST MAC является MAC’ом самого устройства, то процессинг передается в L3 модуль. Следующий шаг - Destination Lookup. Сначала используется L3 Table Lookup, в этой таблице как правило directly attached хосты. Если адрес найден, то выдается index в L3 Interface Table, в котором выходной порт, MAC, VLAN. Если же в L3 table не найден адрес, то делается LPM поиск (Longest Prefix Match). Результат такого поиска - index в L3 Table Lookup таблице, который должен использоваться для форвардинга. После удачного поиска, чип поменяет SA/DA/VID пакета (L2), посчитает FCS, поменяет TTL и IP checksum.

Traffic Manager + MMU¶

Может также называться Buffer Manager. В этом блоке происходят следующие операции:

- Постановка пакетов в очередь

- Их хранение (буферизация)

- Контроль перегрузок

- Диспетчеризация

- Репликация

Он состоит из двух частей - MMU и TM. Первый отвечает за управление памятью и буферами, второй - за QoS и мультикаст.

MMU - Memory Management Unit - компонент чипа, который управляет физической памятью. Одна из его функций аналогична MMU (блоку управления памятью) обычного компьютера - доступ приложений к физической памяти и её защита. Но список его обязанностей гораздо шире, поскольку заточен он на работу именно с пакетами. Он отслеживает как память распределяется между интерфейсами и насколько она занята в каждый момент времени, можно ли поместить пакет в буфер, если да, то в какой, как разбить его на более мелкие ячейки, ну и, конечно, как его оттуда забрать.

TM - Traffic Manager - решает более высокоуровневые задачи - выделение очередей, помещение в них трафика, диспетчеризация, шейпинг, полисинг, управление перегрузками. В общем, всё, что относится к QoS, а так же к мультикасту.

Note

С мультикастом история, право, интересная (как всегда). Репликацией мультикастовых пакетов занимается блок TM. В модульных устройствах это происходит в два этапа: сначала на входном чипе создаётся столько копий, сколько выходных чипов должны получить этот пакет, а затем на выходных чипах ещё столько копий, сколько портов на этой плате должны его получить. Делается это для того, чтобы лишними копиями не загружать фабрику.Любопытный момент с буферизацией и контролем перегрузок: входной чип должен учитывать занятость выходного порта, прежде, чем отправлять пакет, потому что именно входная плата управляет VOQ. Поскольку Traffic Manager оперирует не самими пакетами, а по сути информацией о них, то ему необязательно делать сразу копий по числу выходных портов, а достаточно записать об этом информацию в VOQ.

MMU - это не совсем часть TM - это, скорее, два взаимодействующих друг с другом блока.

Память и буферизация на сетевых устройствах - это настолько масштабная тема, что ей я посвятил отдельную статью, которая выйдет на nag.ru прямо следом за этой. В ней мы разберёмся с устройством и архитектурой памяти, видами и расположением буферов, арбитражем и поднимем самый горячий вопрос современности - что лучше: большие и маленькие буферы.

В разговорах о буферах связка TM+MMU - одни из важнейших блоков ASIC’а (или внешний чип), поэтому к ним мы ещё вернёмся позже.

Egress Match-Action¶

Далее над заголовками пакетов могут быть совершены дополнительные акты - например, выходной ACL, туннельные инкапсуляции, сбор статистики итд.

Deparser¶

К этому моменту на основе результатов обработки в блоках Match-Action сформирован список новых заголовков, и он может воссоединиться с телом пакета. Сам пакет теперь готов в последний путь внутри этого чипа, чтобы выйти через выходной интерфейс.

Кроме того, здесь может собираться дополнительная статистика о длине пакетов и сообщаться блоку TM и зеркалироваться исходящий трафик.

Вышеуказанные стадии могут быть выполнены в пределах одного чипа, а могут быть и разнесены на разные. Так, в случае single-chip-коробки - все они скомпонованы в один кусочек силикона, площадью с фотку на документы. На модульных коробках Parser и Ingress Match-Action - это входной чип коммутации, Egress Match-Action и Deparser - выходной, TM стоит отдельно между чипом коммутации и фабрикой, и может быть разделён на Ingress и Egress. Кроме того в модульных устройствах могут существовать ещё и отдельные чипы Fabric Interface, которые разбивают пакеты на ячейки одного размера и отправляют в фабрику.